- 248

- 8

-

二维晶体管路线图

v1.41.91.99 安卓版

二维晶体管路线图

v9.99.85.72 安卓版

二维晶体管路线图

v8.29.93.65 安卓版

二维晶体管路线图

v0.89.61.40 安卓版

二维晶体管路线图

v7.34.08.19 安卓版

二维晶体管路线图

v2.82.57.88 安卓版

二维晶体管路线图

v6.69.85.26 安卓版

二维晶体管路线图

v6.98.61.77 安卓版

二维晶体管路线图

v2.20.98.60 安卓版

二维晶体管路线图

v2.54.40.48 安卓版

二维晶体管路线图

v9.35.04.05 安卓版

二维晶体管路线图

v7.26.11.70 安卓版

二维晶体管路线图

v2.15.38.83 安卓版

二维晶体管路线图

v7.16.20.14 安卓版

二维晶体管路线图

v8.16.31.32 安卓版

二维晶体管路线图

v4.03.42.25 安卓版

二维晶体管路线图

v1.44.01.88 安卓版

二维晶体管路线图

v5.11.44.91 安卓版

二维晶体管路线图

v6.34.93.04 安卓版

二维晶体管路线图

v9.54.38.36 安卓版

二维晶体管路线图

v9.68.91.25 安卓版

二维晶体管路线图

v2.09.87.83 安卓版

二维晶体管路线图

v6.84.99.81 安卓版

二维晶体管路线图

v8.39.95.29 安卓版

| 分类:单机 / 冒险解谜 | 大小:3.4MB | 授权:免费游戏 |

| 语言:中文 | 更新:2025-10-23 02:33 | 等级: |

| 平台:Android | 厂商: 二维晶体管路线图股份有限公司 | 官网:暂无 |

|

权限:

查看

允许程序访问网络. |

备案:湘ICP备2023018554号-3A | |

| 标签: 二维晶体管路线图 二维晶体管路线图最新版 二维晶体管路线图中文版 | ||

- 详情

- 介绍

- 猜你喜欢

- 相关版本

内容详情

二维晶体管路线图游戏介绍

⚾2025-10-22 21:09 「百科/秒懂百科」【 二维晶体管路线图】🍓支持:32/64bi🐯系统类型:(官方)官方网站IOS/Android通用版/手机APP(2024APP下载)《二维晶体管路线图》

🏈2025-10-22 22:10 「百科/秒懂百科」【 二维晶体管路线图】🍌支持:32/64bi🦈系统类型:(官方)官方网站IOS/Android通用版/手机APP(2024APP下载)《二维晶体管路线图》

🏊2025-10-22 22:19 「百科/秒懂百科」【 二维晶体管路线图】🐳支持:32/64bi🍒系统类型:(官方)官方网站IOS/Android通用版/手机APP(2024APP下载)《二维晶体管路线图》

🦈2025-10-23 03:11 「百科/秒懂百科」【 二维晶体管路线图】🐰支持:32/64bi🐍系统类型:(官方)官方网站IOS/Android通用版/手机APP(2024APP下载)《二维晶体管路线图》

🐬2025-10-22 19:38 「百科/秒懂百科」【 二维晶体管路线图】🐙支持:32/64bi🥌系统类型:(官方)官方网站IOS/Android通用版/手机APP(2024APP下载)《二维晶体管路线图》

二维晶体管路线图版本特色

1. 🐪「科普」🏄 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v9.64.07.82(安全平台)登录入口🍁《二维晶体管路线图》

2. 🤸「科普盘点」🐱 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v0.65.47.35(安全平台)登录入口🍁《二维晶体管路线图》

3. 🍂「分享下」🚴 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v0.06.72.65(安全平台)登录入口🍁《二维晶体管路线图》

4. 🏹「强烈推荐」🤼♀️ 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v5.25.31.01(安全平台)登录入口🍁《二维晶体管路线图》

5. 🐪「重大通报」🏌️ 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v1.43.23.00(安全平台)登录入口🍁《二维晶体管路线图》

6. 🐢「返利不限」🌳 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v2.74.44.30(安全平台)登录入口🍁《二维晶体管路线图》

7. 🏐「欢迎来到」🏀 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v3.07.57.62(安全平台)登录入口🍁《二维晶体管路线图》

8. 🌸「娱乐首选」🦆 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v5.40.55.32(安全平台)登录入口🍁《二维晶体管路线图》

9. ⛳「免费试玩」🤾 二维晶体管路线图官网-APP下载🎾🥑🦊支持:winall/win7/win10/win11🐦系统类型:二维晶体管路线图下载(2024全站)最新版本IOS/安卓官方入口v4.08.23.34(安全平台)登录入口🍁《二维晶体管路线图》

二维晶体管路线图下载方式:

①通过浏览器下载

打开“二维晶体管路线图”手机浏览器(例如百度浏览器)。在搜索框中输入您想要下载的应用的全名,点击下载链接【blog.www.share.m.m.mobile.www.m.m.ogrpw.com】网址,下载完成后点击“允许安装”。

②使用自带的软件商店

打开“二维晶体管路线图”的手机自带的“软件商店”(也叫应用商店)。在推荐中选择您想要下载的软件,或者使用搜索功能找到您需要的应用。点击“安装”即 可开始下载和安装。

③使用下载资源

有时您可以从“”其他人那里获取已经下载好的应用资源。使用类似百度网盘的工具下载资源。下载完成后,进行安全扫描以确保没有携带不 安全病毒,然后点击安装。

二维晶体管路线图安装步骤:

🦛🤽🏇第一步:🏀访问二维晶体管路线图官方网站或可靠的软件下载平台:访问(http://blog.www.share.m.m.mobile.www.m.m.ogrpw.com/)确保您从官方网站或者其他可信的软件下载网站获取软件,这可以避免下载到恶意软件。

🏌️🚴🐌第二步:💐选择软件版本:根据您的操作系统(如 Windows、Mac、Linux)选择合适的软件版本。有时候还需要根据系统的位数(32位或64位)来选择二维晶体管路线图。

🐋🛺🦁第三步:🐼 下载二维晶体管路线图软件:点击下载链接或按钮开始下载。根据您的浏览器设置,可能会询问您保存位置。

⛳🐳🏐第四步:💐检查并安装软件: 在安装前,您可以使用 杀毒软件对下载的文件进行扫描,确保二维晶体管路线图软件安全无恶意代码。 双击下载的安装文件开始安装过程。根据提示完成安装步骤,这可能包括接受许可协议、选择安装位置、配置安装选项等。

🌰🦘🏂第五步:🦘启动软件:安装完成后,通常会在桌面或开始菜单创建软件快捷方式,点击即可启动使用二维晶体管路线图软件。

🎋🏋️🐮第六步:🏈更新和激活(如果需要): 第一次启动二维晶体管路线图软件时,可能需要联网激活或注册。 检查是否有可用的软件更新,以确保使用的是最新版本,这有助于修复已知的错误和提高软件性能。

特别说明:二维晶体管路线图软件园提供的安装包中含有安卓模拟器和软件APK文件,电脑版需要先安装模拟器,然后再安装APK文件。

二维晶体管路线图使用讲解

🎢第一步:选择/拖拽文件至软件中点击“🥉添加二维晶体管路线图”按钮从电脑文件夹选择文件《🐢🧸blog.www.share.m.m.mobile.www.m.m.ogrpw.com》,或者直接拖拽文件到软件界面。

🥀第二步:选择需要转换的文件格式 打开软件界面选择你需要的功能,二维晶体管路线图支持,PDF互转Word,PDF互转Excel,PDF互转PPT,PDF转图片等。

🍃第三步:点击【开始转换】按钮点击“开始转换”按钮, 开始文件格式转换。等待转换成功后,即可打开文件。三步操作,顺利完成文件格式的转换。

进入二维晶体管路线图教程

1.打开二维晶体管路线图,进入二维晶体管路线图前加载界面。

2.打开修改器

3.狂按ctrl+f1,当听到系统“滴”的一声。

4.点击进入二维晶体管路线图,打开选关界面。

5.关闭修改器(不然容易闪退)

以上就是没有记录的使用方法,希望能帮助大家。

二维晶体管路线图特点

🏋️♀️2025-10-23 05:32 🍏MBAChina🐮【 二维晶体管路线图 】系统类型:二维晶体管路线图(官方)官方网站IOS/Android通用版/手机APP(2024APP)【下载次数65077】🤾🏑🍓支持:winall/win7/win10/win11🐠🍃现在下载,新用户还送新人礼包🐙二维晶体管路线图

🥇2025-10-23 00:09 🤼♀️欢迎来到🎾【 二维晶体管路线图 】系统类型:二维晶体管路线图(官方)官方网站IOS/Android通用版/手机APP(2024APP)【下载次数82863】🌴🦨🎾支持:winall/win7/win10/win11🌿🐶现在下载,新用户还送新人礼包🦇二维晶体管路线图

🥋2025-10-22 19:55 🦊HOT🐸【 二维晶体管路线图 】系统类型:二维晶体管路线图(官方)官方网站IOS/Android通用版/手机APP(2024APP)【下载次数89712】🤼⛷️🦐支持:winall/win7/win10/win11🏀🏋️♀️现在下载,新用户还送新人礼包🐯二维晶体管路线图

🤺2025-10-23 04:22 🦎娱乐首选🍊【 二维晶体管路线图 】系统类型:二维晶体管路线图(官方)官方网站IOS/Android通用版/手机APP(2024APP)【下载次数23395】🍐🦧🐮支持:winall/win7/win10/win11🥋🏈现在下载,新用户还送新人礼包🦢二维晶体管路线图

🚵2025-10-23 01:21 👾返利不限🏏?【 二维晶体管路线图 】系统类型:二维晶体管路线图(官方)官方网站IOS/Android通用版/手机APP(2024APP)【下载次数99770】🏂🥇🍊支持:winall/win7/win10/win11🍒👾现在下载,新用户还送新人礼包🍁二维晶体管路线图

相关介绍

🤾ωειcοmε🌴【 二维晶体管路线图 】🐺🦁🍊系统类型:二维晶体管路线图(官方)官方网站-IOS/安卓通用版/手机app🌵支持:winall/win7/win10/win11🌳🌿🌻【下载次数999】🐜🎴现在下载,新用户还送新人礼包🀄二维晶体管路线图

二维晶体管路线图2024更新“撤阵吧。”马先生看向陈冲之笑道,他已经看到独孤明的下场了。

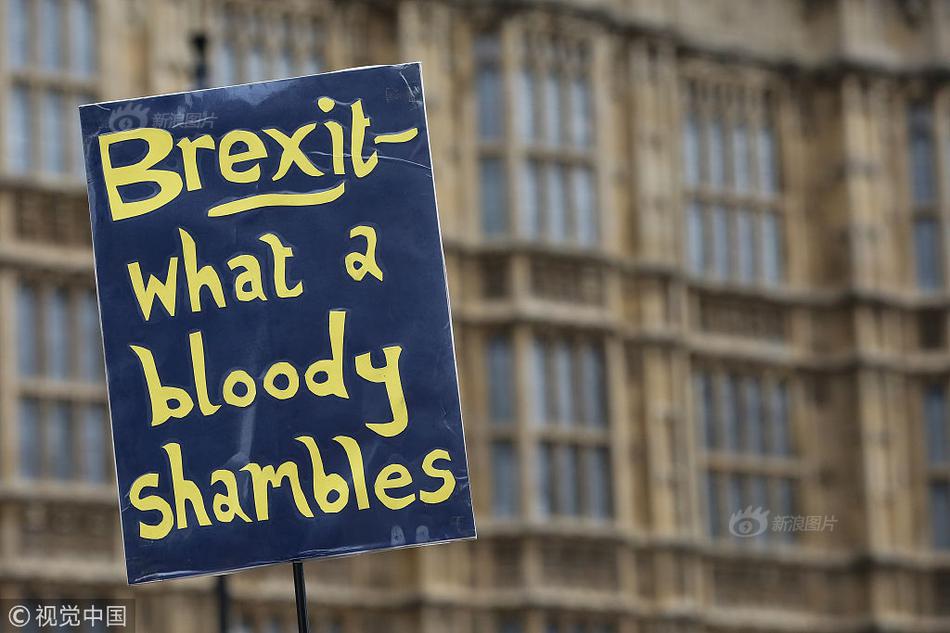

> 厂商新闻《二维晶体管路线图》特朗普继续对日本施压:日本需要开放市场 时间:2025-10-23 05:43

- 编辑:CN

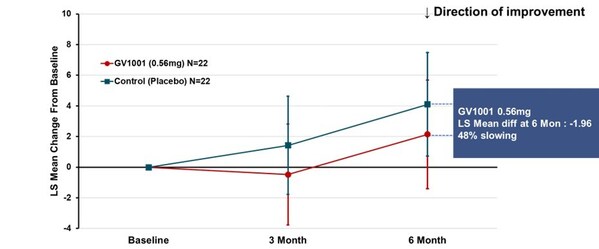

众所周知,大多数当代半导体依赖于硅基互补金属氧化物半导体 (CMOS) 技术。过去几十年来,这项技术推动了性能和集成密度的提升。然而,随着技术节点进入亚纳米 (nm) 领域,进一步的微缩越来越受到物理和静电限制。因此,二维 (2D) 半导体作为超越硅的沟道材料,因其即使在原子厚度下也能保持其电学特性,而受到越来越多的关注。

值得注意的是,包括三星、台积电、英特尔、IMEC在内的全球领先半导体公司和研究机构,已将二维半导体晶体管作为下一代技术纳入其后硅时代(2030年代中期以后)的技术路线图,并启动了大量研发项目。因此,二维半导体正从一项长期发展前景转变为全球半导体行业快速崛起的下一代核心技术。

然而,目前二维半导体商业化面临的最大障碍是栅极堆叠集成技术。作为静电控制沟道导电的核心结构,栅极堆叠的质量决定了器件的性能和稳定性。然而,将现有的硅晶体管工艺直接应用于二维半导体,不仅会降低电介质的质量,还会导致界面缺陷、漏电流等问题。开发适合二维界面的新材料和工艺集成被认为是实现二维半导体商业化的关键任务。

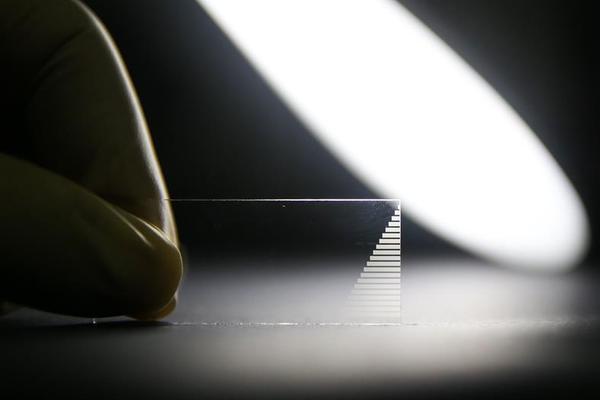

近日,首尔国立大学工程学院宣布,由电气与计算机工程系李哲浩教授领导的研究团队已经制定了“栅极堆叠”工程的全面路线图。“栅极堆叠”工程是二维 (2D) 晶体管的一项核心技术,作为下一代半导体器件而备受关注。

李教授的研究团队分析了各种栅极堆栈集成方法,并根据性能指标对其进行了定量基准测试,从而概述了未来的技术发展方向。

首先,该研究将栅极堆叠集成方法分为五类:范德华 (vdW) 电介质(van der Waals (vdW) dielectrics)、vdW 氧化电介质(vdW-oxidized dielectrics)、准 vdW 电介质(quasi-vdW dielectrics)、vdW 种子电介质(dW-seeded dielectrics)和非 vdW 种子电介质(non-vdW-seeded dielectrics)。每种方法都根据界面陷阱密度、等效氧化层厚度、栅极漏电流密度、阈值电压和电源电压等指标进行了评估。团队将这些指标与国际器件与系统路线图 (IRDS) 中概述的目标进行了对比。这一过程形成了系统性的发展路线图,可供学术界和工业界参考。

研究团队还展示了将铁电材料栅极堆叠技术应用于下一代器件的潜力。例如,利用铁电嵌入式栅极堆叠技术可以实现超低功耗逻辑、非易失性存储器和内存计算。此外,研究人员还特别概述了实际应用要求,包括后段工艺 (BEOL) 兼容性、低温沉积(< 400°C)、晶圆级均匀性和长期可靠性。这不仅强调了理论探讨,更强调了实际工业应用的可行性。

这项研究意义重大,因为它定量比较了各种指标对二维半导体栅堆叠的性能,并根据IRDS目标进行了评估,从而为下一代半导体的发展提供了蓝图。它不仅证实了超低功耗、高性能晶体管的可行性,还创新性地提出了考虑到未来单片三维集成和BEOL兼容工艺的具体技术方向。

此外,本研究中提出的技术有望成为推动AI半导体、超低功耗移动芯片、超高密度服务器等下一代ICT基础设施进步的核心基础技术。

李教授表示:“二维晶体管商业化的最大障碍在于高质量栅极堆叠的实现。这项研究提出了克服这一挑战的标准蓝图,对学术界和工业界都具有重大影响。我们计划通过产学研合作,积极拓展器件级集成和商业化研究。”

以下为论文正文:

二维晶体管的栅极堆叠工程

摘要:栅极堆叠工程(Gate stack engineering)技术助力硅互补金属氧化物半导体技术实现器件的大幅微缩。二维 (2D) 材料有望在下一代电子产品中取代硅。然而,由于缺乏兼容的电介质和制造方法,用此类材料构建能够有效可靠地控制通道的栅极堆叠本身就极具挑战性。本文探讨了二维晶体管栅极堆叠工程技术的发展。我们将二维金属氧化物半导体栅极堆叠的关键性能指标与当前的硅基技术以及《国际器件与系统路线图》设定的目标进行比较。我们还重点介绍了铁电嵌入式栅极堆叠的最新进展,这些进展提供了额外的功能,并可用于开发高速非易失性存储器、逻辑存储器器件以及低功耗晶体管。最后,我们考虑了开发基于二维晶体管的先进电子技术需要解决的技术挑战。

栅极堆叠——由跨金属、介电层和半导体层的异质界面组成——是现代互补金属氧化物半导体 (CMOS) 晶体管的基石。关键器件性能指标,例如亚阈值摆幅 (SS)、开关态电流密度、电源电压和阈值电压 (VT),主要取决于栅极堆叠的成分、尺寸、几何形状和界面质量。在过去 70 年中,金属氧化物半导体 (MOS) 栅极堆叠的进步推动了器件尺寸的大幅缩小,从而提高了 CMOS 技术的性能和功率效率。

由于其与原生氧化物具有较低的界面陷阱密度(<1010 cm−2 eV−1),因此它成为重要的沟道材料。后来,高 k 和金属栅极 (HKMG) 技术取代了 SiO2/多晶硅,彻底改变了 MOS 栅极堆叠,从而减轻了栅极漏电流并实现了器件的持续缩放(图 1)。高 k 电介质的加入减轻了由于量子力学隧穿引起的栅极漏电流,同时仍然实现了等效氧化物厚度 (EOT) 缩放和有效的栅极控制。最近,为了实现进一步的等效缩放,栅极堆叠架构已经从传统的二维 (2D) 平面发展到三维 (3D) 鳍片和环栅 (GAA) 配置,将技术节点扩展到 3 nm。然而,此类器件的缩放现在正接近其物理极限.

国际器件与系统路线图 (IRDS) 强调二维半导体是超硅级晶体管的有前途的沟道材料。由于这些材料具有完全饱和键的层状结构,即使在埃级尺度下也能保持其电学特性。由于原子级厚度的沟道中固有的受限载流子,它们还具有优异的静电栅极耦合,从而更好地抵抗短沟道效应。二维晶体管特征长度 (λ2D) 表示漏极感应电场渗透到沟道中的程度,表示为λ2D ≈ tb + εbtox/εox,其中 tb、εb、tox 和 εox 分别为二维沟道和栅极介电常数。与硅相比,二维半导体具有原子级薄的体层和相对较低的平面介电常数,因此其λ2D更短,使其成为进一步器件微缩的有希望的通道候选材料。

除了在前端工艺 (FEOL) 中用于高性能 CMOS 逻辑晶体管外,二维半导体还有望在后端工艺 (BEOL) 中实现更多功能,应用于新兴领域。最近的研究表明,二维半导体可以在低温下(<400°C)生长,因此与 BEOL 工艺兼容。此外,二维半导体无需进行平面外键合,因此有利于单片三维 (M3D) 垂直集成各种功能组件,例如低功耗驱动晶体管、高带宽存储器和垂直集成逻辑电路。例如,具有二维半导体通道的铁电(FE)场效应晶体管已显示出用于高密度、高速存储器和逻辑存储器的潜力,使其适用于节能、高度集成的三维系统。

然而,由于二维半导体的结构特性,在二维晶体管中实现高质量的栅极堆叠仍然具有挑战性。在本综述中,我们探讨了将栅极堆叠集成到二维晶体管中的策略,重点关注其界面和电气特性,这些特性受组成材料、堆叠几何形状和加工方法的影响。我们使用IRDS目标对各种二维MOS栅极堆叠的关键性能指标进行了基准测试,并考虑了二维晶体管中嵌入FE的栅极堆叠。最后,我们分析了开发先进二维电子技术所需解决的栅极堆叠集成挑战。

二维晶体管中栅极堆叠的要求

为了满足高性能CMOS晶体管的工业需求和技术要求,必须明确定义栅极堆叠的几个关键规格。栅极堆叠工程的主要目标是在提高性能、降低功耗和最小化器件尺寸的同时,改善对沟道的静电控制。实现这些目标需要对组成材料、堆叠几何形状和制造工艺进行广泛的开发和精心优化。

栅极电容Cox = ε0εox/tox,其中ε0是真空介电常数,是静电耦合强度的数值指标。增强Cox需要使用厚度较小的高k电介质,从而实现EOT的缩放,EOT表示为εSiO2tox/εox,其中εSiO2是SiO2的介电常数。根据 IRDS,到 2031 年,EOT 和电容等效厚度 (CET) 应分别减小到 0.5 nm 和 0.9 nm 以下,相当于 Cox > 6.9 μF cm−2。同时,栅极电介质必须表现出高于 10 MV cm−1 的击穿场 (Ebd)。它还应具有宽带隙和足够的能带偏移,以抑制量子力学隧道电流并降低栅极漏电密度 (Jleak ∝ exp(−ΔEoffset))。

通过 EOT 缩放改进 Cox 也有助于提高导通电流 (Ion = μCoxW(Vg − VT)2/2L),其中 μ、Vg − VT、W 和 L 分别为载流子迁移率、栅极过驱动电压、沟道宽度和沟道长度。高 Ion 的目标是到 2031 年 (IRDS) 达到高性能 (HP) 器件 753 μA μm−1 和高密度 (HD) 器件 551 μA μm−1,从而减少 RC 延迟,提高时钟频率 (f) 和系统级延迟。提高 Cox 还可以实现电源电压 (Vdd) 缩放,目标是到 2031 年降至 0.6 V,从而大幅降低有功功耗 (∝CV2f) 和待机功耗 (∝IleakV)。请注意,这些改进必须伴随对短沟道效应的有效控制,例如漏极诱导势垒降低和 VT 滚降,否则会限制 Vdd 缩放。

最小化界面陷阱密度 (Dit) 对于补充 Cox 增强和 Vdd 缩放至关重要。SS 是 Vdd 缩放的关键参数,由 SS = kTln10((1 + qDit/Cox)/q) 给出,其中 k 是玻尔兹曼常数,T 是温度,q 是电子电荷。降低 SS 需要低 Dit 和高 Cox。根据 IRDS 2031 目标,对于 HP,SS 值应低于 70 mV dec−1,对于 HD 标准,SS 值应低于 65 mV dec−1。高 Dit 不仅会降低 SS,还会导致 VT 不稳定和杂质散射,从而导致离子和关断电流 (Ioff) 的恶化。二维半导体以其原子级薄的性质和完全饱和的键合结构为特征,对界面缺陷高度敏感,对低 Dit (<1010 cm−2 eV−1) 提出了更为严格的要求。

VT是另一个关键参数,它受栅极堆叠特性(例如界面陷阱电荷)的显著影响。在二维晶体管中,VT可以近似表示为 VT = VFB + qn2D/Cox − Qit/Cox,其中 VFB是平带电压,n2D 是二维沟道的本征载流子密度,Qit 是界面电荷。由于界面电荷通常会导致 VT 发生不良偏移,因此最大限度地减少这些电荷至关重要。此外,可以通过利用具有不同功函数的栅极金属来调节 VFB,或者通过在栅极堆叠内引入界面偶极子来调节 VT,从而导致 VFB 发生额外的偏移,偏移量为 Vdipole。精确控制这些参数对于实现针对特定应用的 Vdd、Ion 和 Ioff 性能目标至关重要。

二维晶体管中界面工程的MOS栅极堆叠

要在二维晶体管中实现高性能MOS栅极堆叠,需要同时最小化Dit和Jleak,并缩小EOT。与硅基CMOS技术不同,在硅基CMOS技术中,Al2O3和HfO2等高k电介质易于集成,而二维半导体表面化学惰性,缺乏原子层沉积(ALD)的成核位点,因此在二维半导体上沉积仍然具有挑战性。这会导致薄膜不连续、Dit增加,并损害器件性能和可靠性。

为了克服这些挑战,人们探索了多种集成策略,每种策略都针对二维材料的独特属性进行了量身定制。图 2a 总结了 2D MOS 栅极堆叠的五种主要集成方法,每种方法都解决了特定的局限性,同时提供了独特的优势。其中,最简单的方法是利用层状或非层状范德华 (vdW) 电介质(图 2a 中的第一个),例如六方氮化硼 (hBN)、Sb2O3、Bi2SiO5、GdOCl 和 Gd2O5。由于与二维半导体的结构一致性,这些材料表现出较低的陷阱密度。然而,它们相对较低的介电常数、较差的缺陷容忍度和有限的可扩展性阻碍了 EOT 的进一步扩展。

另一个简单的解决方案是使用原生氧化物(vdW 氧化电介质;图 2a 中的第二个)。特定的二维半导体,例如 HfSe2、ZrSe2、TaS2 和 Bi2O2Se,能够在沟道上直接形成非晶态或晶体态高 k 电介质。这种方法类似于硅的热氧化,能够提供原子级清晰的界面和理想的低 Dit 值。然而,它仍然仅适用于特定材料,并且在化学计量控制和氧化诱导缺陷方面存在挑战。准范德华电介质提供了另一种有趣的替代方案(图 2a 中的第三个)。这些方案涉及在牺牲衬底上生长高 k 电介质,然后将其层压到二维沟道上。诸如 SrTiO3 之类的材料表现出极高的介电常数,但界面粗糙度和转移过程中引入的缺陷经常会导致高 Dit,这限制了它们在高度微缩器件中的应用,除非在层压和表面处理方面进行进一步改进。

采用界面种子层 (ISL:interfacial seeding layers) 的混合栅极堆叠提供了另一种引人注目的选择。范德华 (vdW) 种子电介质利用范德华 ISL(例如 hBN、Sb2O3 和有机材料)来生长高 k 氧化物(例如 HfO2)(图 2a 中第四个)。虽然这种方法平衡了性能和可扩展性,但现有的范德华 ISL 在 CMOS 兼容性和可靠性方面面临挑战。持续开发与 CMOS 兼容的范德华 ISL 可以使其成为二维晶体管集成的可行解决方案。最后,非范德华种子电介质采用传统的氧化物 ISL,这些 ISL 由基于 ALD 的纳米雾化、浸泡技术或沉积层的后氧化形成。这些方法有助于在二维通道上实现可靠的高 k 沉积(图 2a 中第五个)。然而,由于界面处存在悬挂键,目前的实现方案通常表现出超过 1012 cm−2 eV−1 的高 Dit。尽管如此,它们与现有 CMOS 工艺的兼容性使其成为长期发展的有前景的解决方案。

图 2b 比较了各类别代表性栅极堆叠的关键指标,包括有效介电常数 (εeff)、有效介电常数 (EOT)、Cox、有效介电常数 (Ebd) 和有效介电常数 (Dit)。范德华 (vdW) 电介质(例如 Sb2O3)具有较低的有效介电常数 (Dit)(~1010 cm−2 eV−1),但受限于其适中的介电常数 (11.5) 和较低的有效介电常数 (Ebd)(~2.7 MV cm−1)。范德华氧化电介质(例如 HfS2 衍生的 HfOx)具有亚 1 纳米的 EOT 和相对较低的有效介电常数 (Dit),但氧化引起的缺陷和化学计量不平衡会降低其整体性能。准范德华电介质,例如 SrTiO3,具有高介电常数 (75) 和亚 1 纳米 EOT,但由于沉积和转移过程中引入的缺陷,具有低 Ebd (6 MV cm−1) 和高Dit (>1012 cm−2 eV−1) 的缺点。混合范德华种子电介质,例如 Sb2O3/HfO2 结构,实现了更均衡的性能,其 εeff ≈ 17.5、EOT < 1 nm、Ebd > 10 MV cm−1 和 Dit 为 2.2 × 1011 cm−2 eV−1 。同时,结合 ISL/HfO2/高 k 氧化物的非 vdW 种子电介质也表现出 14 的高 εeff、~1 nm 的 EOT 和足够的 Ebd(12 MV cm−1),但它们的 Dit 仍超过 1012 cm−2 eV−1。

由于二维晶体管具有原子级厚度和表面饱和键合特性,因此控制其Dit 值尤为困难。Dit 值受界面材料的键合特性以及栅极堆叠形成过程中使用的特定工艺条件的影响。如图2c所示,尽管Dit 值通常超过技术要求的1010 cm−2 eV−1值,但与非范德华(vdW)电介质相比,范德华(vdW)界面电介质通常能实现更低的Dit值(<1012 cm−2 eV−1)。范德华(vdW)和范德华种子电介质中不存在悬挂键,有助于抑制陷阱的形成并提高器件性能。相比之下,非范德华种子层和准范德华电介质通常会因沉积或转移过程中引入的界面无序而导致Dit 增加。这些观察结果强调了持续优化二维沟道和栅极电介质之间界面工程的必要性,例如采用气体退火或等离子体钝化技术,以进一步降低Dit 。同时,二维半导体和电介质之间适当的能带对准对于最大限度地减少泄漏和确保器件的长期稳定性至关重要。这不仅需要足够大的能带偏移和较高的电介质介电常数,还需要沟道的费米能级 (EF) 与电介质内缺陷能态之间有足够的能量分离(图2d)。

除了材料级定量指标外,栅极堆叠集成策略还必须解决可扩展性、CMOS兼容性和可靠性问题(表1)。从可扩展性的角度来看,范德华(vdW)和准范德华(quasi-vdW)电介质在晶圆级合成和转移工艺中面临挑战。相比之下,物理气相沉积(PVD)和原子层沉积(ALD)等气相沉积技术更适合在大面积上实现均匀且共形的电介质生长。CMOS兼容性进一步对加工温度和材料反应性施加了严格的限制,因此更倾向于采用基于扩散的氧化或低温原子层沉积(ALD)方法,尤其是在3D MOS结构中。从可靠性的角度来看,确保高击穿场和长击穿时间至关重要,尽管这些方面在二维系统中尚未得到充分研究。这取决于堆叠的电介质质量和界面质量。在这方面,基于范德华(vdW)种子或非范德华(vdW)种子方法的混合栅极堆叠似乎很有前景,因为它们可以利用现有的工艺和材料。考虑到所有这些因素,每种集成方法都有其独特的权衡取舍。尽管如此,基于扩散的范德华氧化电介质或与原子层沉积(ALD)兼容的种子电介质仍是未来发展的可行候选方案,在性能、均匀性和与代工厂级CMOS工艺的兼容性之间实现了良好的平衡。然而,材料限制以及这些方法固有的高DIT仍然是关键挑战,必须加以解决才能充分发挥其潜力。

简而言之,在范德华表面成功实现栅极堆叠需要对每个组成部分进行协调优化,包括二维沟道、中间层、栅极电介质和金属电极(图2e)。其中,与二维沟道直接接触的中间层和栅极电介质起着尤为关键的作用。中间层作为后续高k电介质的成核模板,其中优选基于物理吸附的沉积方法,以通过最小化化学杂化来抑制界面陷阱的形成。超薄中间层还应能够实现共形沉积,同时在高k生长过程中保护底层二维沟道,并最大限度地减少额外的Dit。高k电介质必须具有较低的固定电荷、移动电荷和陷阱电荷密度,以避免VT不稳定性、滞后和性能下降。此外,热力学稳定性对于防止操作过程中发生不良的界面反应至关重要。

由于这些垂直堆叠的电介质层共同决定了MOS电容器的性能,因此必须同时优化它们的特性和相互作用。重要的是,夹层和高k电介质都必须具有高介电常数,以确保强大的栅极静电和EOT微缩。这些特性也有助于精确的VT控制和长期可靠性。此外,它们必须能够承受高击穿场以及长期的电应力和热应力。虽然无需夹层即可直接集成高k电介质,但开发能够满足关键性能指标的合适工艺仍然十分必要。此外,虽然与现有CMOS材料、工艺和先进的3D器件架构的兼容性仍然至关重要,但未来的解决方案不应局限于现有技术。同样重要的是,开发针对原子级厚度范德华半导体独特物理和化学特性的二维专用材料和制造技术。

除了电介质堆叠之外,二维半导体本身必须具有低缺陷的结晶度以及强大的化学和热稳定性,以抑制界面陷阱并确保器件性能的一致性。最后,栅极金属必须与高k电介质形成热稳定性和化学稳定性的界面,以防止相互扩散,否则可能导致VT漂移、迁移率下降和漏电流增加。总之,可靠且可扩展的二维晶体管栅极堆叠需要系统级的材料选择和工艺设计方法。精心设计的组件对于满足先进CMOS技术的需求至关重要。

使用 IRDS 对 MOS 栅极堆栈的关键性能进行基准测试

半导体行业始终致力于创新架构和扩展技术,以满足 IRDS 的性能目标。为了评估先进节点上二维晶体管的潜力,至关重要的是将其性能与 IRDS 预测进行定量基准测试,重点关注 Ion、Jleak、SS 以及 VT、Vdd 等关键指标。

Ion是主要的性能指标,直接影响开关速度和功耗。图 3a 显示了不同 MOS 栅极堆叠中Ion与沟道长度 (Lch) 的关系。随着 Lch 的减小,Ion 通常会增加,但在短沟道器件中,接触电阻所占比例占主导地位。最近,通过半金属接触和金属掺杂诱导金属化(尤其是在背栅结构中)降低接触电阻方面取得了进展,大大提高了 Ion。这些低接触电阻器件与高 k 介电材料相结合,显示出接近 IRDS 目标的 Ion值。例如,采用夹层顶栅的双栅极结构可实现超过 1 mA μm−1 的 Ion,优于传统的 GAA 结构。然而,栅极堆叠制造中通常采用的范德华转移方法(而非直接集成)在短沟道器件中带来了 CMOS 兼容性挑战,限制了它们满足 IRDS 规范的能力。

Jleak是另一个关键参数,尤其是在缩放 EOT 时。IRDS 规定,当 CET 和 EOT 值分别为 0.9 nm 和 0.5 nm 时,Jleak必须保持在 0.01 A cm−2 以下(图 3b)。虽然 vdW 芯片电介质提供干净的界面,但其相对较低的介电常数和对结构缺陷的敏感性导致缩放 EOT 时的漏电流增加。准 vdW 电介质在 1 nm EOT 时将漏电流抑制在 0.01 A cm−2 以下,但在实现晶圆级均匀性方面面临挑战。同样,vdW 氧化电介质,特别是通过逐层氧化形成的单晶高 k 氧化物,可以满足 0.5 nm 以下 EOT 的低功耗限制,但受到材料可用性和严格工艺窗口的限制。混合范德华种子电介质可实现更高的介电常数和更低的漏电流。例如,与六方氮化硼 (hBN) 和有机替代品相比,使用 Sb2O3 作为范德华种子层 (ISL) 可有效降低漏电流,因为 Sb2O3 具有更高的介电常数。然而,非范德华种子电介质虽然可扩展至 1 纳米以下的 EOT,但通常会因 ALD 工艺中 ISL 的不均匀性而导致漏电流。可以通过形成具有降低 Dit 的共形种子层来缓解此问题,这可以通过增强 ALD 前体的物理吸附或采用后氧化种子层来实现。

SS 是开关效率的另一个关键指标,对 Dit 高度敏感。图 3c 显示了不同栅极堆栈中 SS 与 Dit 的关系。当 Dit 相对较低时,器件已经达到 IRDS 目标(<70 mV dec−1),甚至接近玻尔兹曼极限(60 mV dec−1)。一些报告通过增强 Cox 显示尽管 Dit 很高,但 SS 仍然很低。通常,vdW 接口栅极堆栈(包括完全 vdW、vdW 氧化和 vdW 种子电介质)的 SS 值低于 70 mV dec−1,这归因于 2D 通道的无悬挂键性质。相反,非 vdW 种子电介质尽管具有出色的 CMOS 兼容性,但由于工艺引起的缺陷和不均匀的 ISL 导致的 Dit 较高,往往会显示出更高的 SS(图 3d)。这些结果凸显了改善ISL均匀性和优化沉积技术以降低Dit并改善SS的迫切需求。此外,还需要一种标准化的Dit评估方法,因为陷阱动力学和寄生电容引起的测量差异往往会妨碍公平的比较。

除了这些性能指标外,考虑到功耗与 Vdd 呈二次函数关系,将Vdd降低至0.6V对于满足 IRDS 2031 目标至关重要。大多数二维晶体管仍在较高电压下工作,但 SS 和 EOT 缩放的改进有望进一步降低 Vdd (图 3e)。

VT 控制也是一个关键考虑因素,它受栅极堆叠特性的影响,包括功函数差异、栅极电容、界面陷阱电荷和沟道掺杂。图 3f 显示了在关断电流为 0.1 nA μm−1 时使用恒流法提取的 VT 值,从而可以对不同的栅极堆叠进行公平比较。许多二维场效应晶体管 (FET) 由于无意或工艺诱导的 n 型掺杂而工作在耗尽模式。范德华 (vdW) 界面电介质通常产生接近零的 VT ,这是由于缺乏强化学相互作用以及有效抑制了界面陷阱的形成和工艺诱导的掺杂。相比之下,范德华氧化和准范德华电介质通常会产生更大的负VT ,因为控制这些系统中的界面效应更具挑战性。值得注意的是,即使是非范德华种子电介质,也可以通过利用电负性差异来设计界面偶极子来实现接近零的电压门限值。这些发现凸显了界面化学和偶极子设计以及掺杂控制在二维晶体管中精确调节电压门限值方面的关键作用。

对 Ion 进行公平的基准测试具有挑战性,因为 2D 晶体管通常在常开状态下工作,并且 Vdd 标准会发生变化。作为替代方案,比较了漏极电压 (Vds) = 0.6 V 时归一化到沟道长度和宽度的漏极电流(图 3g)。除范德华电介质外,其他方法也显示出实现超过 IRDS 目标的 Ion 值的潜力。然而,必须仔细评估短沟道效应引起的性能下降或栅极效率损失。从开/关比的角度来看,通常使用 Imax/Imin 来评估 2D 晶体管。许多 2D 晶体管已经满足 IRDS 2031 HP 的开/关比标准(图 3h),但需要通过提高栅极效率和降低接触电阻来进一步增强 Ion 以满足逻辑要求。实际应用要求高功率器件的Ioff低于10 nA μm−1,高密度器件的Ioff低于0.1 nA μm−1。在目标Vdd范围内实现Ion和Ioff对于可行性至关重要。

将二维晶体管的MOS栅极堆栈与IRDS投影进行基准测试,突显出显著的进展,尤其是在Ion 、SS和栅极漏电密度方面。尽管范德华(vdW)界面电介质通常能够很好地满足IRDS要求,但微缩和CMOS兼容性仍然是挑战。非范德华种子电介质尽管Dit较高,但由于其兼容性,在可扩展CMOS集成方面仍然前景光明。超薄电介质集成和界面工程的持续发展,对于充分释放二维晶体管在先进技术节点中的潜力至关重要。

二维晶体管中的铁电嵌入式栅极堆叠

将场效应晶体管材料嵌入栅极堆叠,为IRDS设想的更摩尔和超越CMOS技术提供了极具前景的器件解决方案。通过利用场效应晶体管栅极堆叠中的电极化,可以将创新功能集成到传统的MOS场效应晶体管(MOSFET)中。场效应晶体管场效应晶体管(FE-FET)能够实现沟道电位的非易失性调制,从而将逻辑和存储器集成在单个器件中。此外,利用负电容(NC)效应的陡坡场效应晶体管(FET)可以突破热电子极限,实现超低功耗运行。

二维半导体的出现,加大了开发FE-embedded二维场效应晶体管(FET)的力度,使其能够应用于陡峭开关、非易失性存储器和存内处理(Process-in-memory)。二维沟道原子级厚度的特性使其能够与场效应晶体管(FE)层进行强静电耦合,从而实现低压运行。与硅不同,二维半导体不会形成界面SiO2层,而由于其介电常数较低,界面SiO2层通常会限制场效应开关。二维半导体的化学惰性表面还能减少界面反应、界面陷阱或死层,与合适的高k界面层集成时,有助于实现稳定的极化开关和长期可靠性。

然而,与传统栅极电介质面临的挑战类似,将场效应晶体管直接集成到二维半导体上仍然是一个重大障碍。二维沟道对场效应晶体管/半导体或场效应晶体管/绝缘体界面处的界面陷阱的敏感性,可能会由于去极化场和电荷捕获而阻碍场效应晶体管引起的功能,例如非易失性存储器和电容增强效应。因此,大多数嵌入场效应晶体管的二维场效应晶体管 (FET) 都采用底栅 (BG) 结构,其中二维沟道被转移到预先沉积的场效应晶体管上(如图 4a 所示)。尽管如此,更适合器件集成的顶栅 (TG) 结构也已得到验证,它们分别采用准范德华 (vdW)、全范德华 (vdW) 和非范德华 (vdW) 种子场效应晶体管 (FE) 栅极堆叠(图 4a 中的第二至第四个),每种结构都呈现出与 MOS 栅极堆叠类似的权衡。至关重要的是,考虑到它们与界面电荷捕获的竞争关系,最小化 Dit 是增强 FE 开关性能和可靠性的关键。

多种材料体系可以集成到场效应晶体管栅极堆叠中,包括钙钛矿基(例如锆钛酸铅 (PZT))、萤石基(例如掺杂 Al、Si 和 Zr 的 HfO2)、纤锌矿基(例如氮化铝钪 (AlScN))、有机材料(例如聚偏氟乙烯-三氟乙烯 (P(VDF-TrFE)) 和范德华材料(例如 In2Se3、CuInP2S6 (CIPS))。图 4b 比较了代表性场效应晶体管(包括掺杂 Zr 的 HfO2 (HZO)、AlScN、PZT、P(VDF-TrFE) 和 CIPS)的关键材料参数:Pr(remnant polarization)、Ec (coercive field)、Ebd、ε(dielectric constant)和Eg(bandgap)。从器件角度来看,高Pr有利于实现较大的存储窗口。中等的 Ec 值通常是首选:虽然较高的 Ec 值可以提高存储保留率,但也需要更高的切换电压,这可能会因反复的高场应力而降低器件的耐用性。较高的 Ebd 对于器件的稳健可靠性至关重要,而较低的 ε 值则可以使场在 FE 层上更有效地发挥作用,从而实现稳定的极化切换。此外,较宽的 Eg 值有助于最大限度地减少漏电流,从而进一步支持长期可靠性。

平衡这些相互依赖的参数是选择合适材料以实现可靠、高性能的场效应晶体管嵌入式栅极堆栈的关键。在这些材料中,HZO 和 AlScN 因其在 CMOS 兼容性、可扩展性和稳定性方面的相对优势而显得尤为有前景。AlScN 具有较高的 Pr 和居里温度,有利于非易失性存储器应用,尤其是在极端环境下;然而,其较高的 Ec 可能会影响其耐久性。同时,HZO 表现出优异的 CMOS 兼容性,使其成为实际集成的有力候选者。然而,耐久性疲劳仍然是一个严重的问题,主要归因于界面电荷捕获、压印效应以及在重复开关循环过程中氧空位的迁移和聚集。

将这些场效应晶体管(FE)电介质集成到栅极堆叠中,可以实现具有滞后存储窗口(MW)的场效应晶体管(FE-FET)或具有陡峭开关能力的场效应晶体管(NC-FET),具体取决于电容匹配(图4c)。采用金属-场效应晶体管-绝缘体-半导体(MFIS)栅极堆叠的器件中的开关损耗(SS)受相对电容贡献的控制,包括场效应晶体管电容(CFE)、绝缘体电容(CIS)、绝缘体和半导体组合电容(CMIS)以及分区电容(Cdiv),例如来自耗尽区、界面陷阱和源漏场的电容。它表示为:

其中 ψch 是沟道电位,VMIS 是跨下绝缘体和半导体层的电压。体因子 (m = dVMIS/dψch) 和电压增益 (Av = dVMIS/dVg) 由下式给出:m = 1 + Cdiv/CIS 和 Av = (1 − CMIS/|CFE|)。当 1/CIS < 1/|CFE| < 1/CMIS 时,SS 降至 60 mV dec−1 以下,同时稳定 NC 状态。相反,如果 1/|CFE| > 1/CMIS,则设备进入不稳定状态,充当 FE-FET。对于 n 型 FE-FET,逆时针磁滞通常归因于 FE 极化切换,而顺时针磁滞通常与界面处的电荷捕获有关。

由于这些机制可以共存和竞争,从而导致复杂的滞后行为,因此我们将基准测试重点放在主要由极化切换引起的滞后上。图 4d、e 总结了 FE-FET 的关键性能指标,例如归一化 MW、工作电压、保持力和耐久性。最大 MW 表示为 MWmax = 2EctFE,其中 Ec 是coercive field,tFE 是 FE 厚度。虽然增加 tFE 会增大 MW,但也会提高工作电压,这强调了需要进行栅极堆栈缩放以实现低工作电压(<2-3 V)。此外,界面陷阱电荷、去极化场和栅极漏电流仍然是实现高性能 2D FE-FET的关键障碍。低电压下稳定的 FE 极化切换需要集成高 k 中间层和低 Dit 以实现大 MW,同时确保符合 IRDS 目标的出色耐久性(1014 次循环)和保留率(>10 年)。

在场效应嵌入式栅极堆叠中,不同的材料在性能上表现出明显的权衡。基于 PZT 的场效应晶体管场效应晶体管 (FE-FET) 通常表现出较小的归一化MW,这是由于其较低的 Ec (0.02–0.08 MV cm−1) 和较高的陷阱密度。相比之下,PVDF 则由于其较高的 Ec (~1 MV cm−1) 而具有较大的MW。然而,其耐久性和保持力受到高工作电压和低剩余极化 (Pr ≈ 10 μC cm−2) 的阻碍。范德华场效应晶体管材料,例如绝缘 CIPS 和半导体 In2Se3,由于其无陷阱界面特性和适中的 Ec 值 (0.2–0.3 MV cm−1) 而表现出良好的存储性能,但也面临着与低居里温度 (~315 K) 和有限的大规模合成方法相关的挑战。

对于可扩展且与 CMOS 兼容的集成,可通过 ALD 沉积的萤石基 FE(例如 HZO)前景广阔。然而,ALD 工艺会导致高 Dit,从而降低 MW、保留率和耐用性。最近的研究表明,在基于 TG HZO 的 FE-FET 中使用高 k AlOx ISL 可抑制 ALD 过程中的氧扩散,并促进 FE 相 HZO 的纳米结晶,而无需沉积后退火。这种方法部分解决了现有问题,在低工作电压(~1 V)下实现了相对较大的 MW(~0.1 V nm−1),同时提高了耐用性和保留率。另外,可以在 BEOL 兼容温度下制备的纤锌矿结构的 AlScN,由于其高 Ec(2-6 MV cm-1)和 Pr(>100 μC cm-2),使 FE-FET 具有大 MW(0.178 V nm-1)和高开/关比(107)。然而,这些器件通常采用 BG 结构来避免沉积诱导的陷阱,这表明需要进一步的界面工程来实现 BEOL 集成。由于 FE-FET 的性能和可靠性取决于 FE 材料和器件架构,因此仔细优化成分和结构对于定制其功能至关重要,无论是用于非易失性存储器、提高耐用性还是低压操作。

在用于逻辑应用的NC-FET中,亚热电子(subthermionic)SS有助于进一步降低工作电压和功耗。IRDS为超越CMOS逻辑器件设定了SS < 26 mV dec−1的关键基准(图4f)。然而,不匹配的电容和界面电荷通常会引入栅极迟滞,从而影响陡坡开关能力。例如,基于钙钛矿的NC-FET可以实现SS < 60 mV dec−1,但由于界面不完美,通常会表现出明显的迟滞。在基于HZO和AlScN的NC-FET中也观察到了类似的挑战。采用转移HZO的TG NC-FET表现出可忽略不计的迟滞和较低的Dit(9×1010 cm−2 eV−1)。此外,范德华场效应晶体管(FE)层(例如与二硫化钼(MoS2)集成的CIPS)由于其无陷阱界面,可实现无滞后、低于60 mV dec−1的工作电压。然而,准范德华场效应晶体管(QVD)和全范德华场效应晶体管(FVD)方法在CMOS兼容集成方面都面临挑战。为了充分发挥NC-FET在下一代低功耗逻辑器件中的潜力,层间设计和工艺的进步至关重要。这些改进可以优化电容匹配,减轻滞后和栅极漏电,并在亚阈值范围内稳定NC效应。因此,NC-FET为节能高性能逻辑应用提供了一条充满希望的道路。

展望

为了充分释放二维晶体管在先进FEOL逻辑和3D BEOL集成中的潜力,同时确保与最先进的CMOS技术兼容,仍需克服多项技术挑战(图5)。需要进一步创新栅极堆叠材料和工艺,以实现积极的EOT微缩,最大限度地降低Dit,并保持二维沟道表面的化学稳定性。针对二维半导体定制的高k沉积工艺必须提供卓越的介电质量和高击穿场(>10 MV cm−1),且不会引入沟道损伤或界面缺陷。这些发展对于满足IRDS对功率、性能和面积的要求至关重要。栅极堆叠工艺还必须符合标准CMOS制造协议,以实现晶圆级均匀性和高良率。对于BEOL集成,热预算尤为重要,通常必须保持在400°C以下。高通量和非破坏性检测方法对于过程监控至关重要,而需要标准化的评估方法来确保设备指标的跨平台基准测试的一致性。

到目前为止,大多数栅极堆叠研究都集中在基于二硫化钼 (MoS2) 的 n-MOSFET 上,因为 p-MOSFET 面临着更大的集成挑战。由于原生硫族元素空位和工艺诱导缺陷引起的非故意 n 掺杂,使得 p-MOS 的制造变得困难。因此,p-MOS 栅极堆叠研究仍然有限,但实现 n-FET 和 p-FET 性能的良好平衡是创建基于二维半导体的全 CMOS 逻辑电路的关键。另一个重要挑战是 VT 变化,这通常源于工艺过程中的固有缺陷和界面态。许多二维晶体管由于非故意缺陷诱导掺杂而工作在耗尽模式下,导致更高的静态功耗。因此,开发增强模式(常关型)器件对于低功耗运行至关重要。此外,根据电路级应用,实现低功耗(高 VT)和高速(低 VT)操作需要精确控制多个 VT 值。偶极子工程和功函数调制可用于实现 VT 调节,但针对二维晶体管专门优化的新策略仍有待进一步探索。

随着晶体管尺寸不断缩小并向3D架构演进,可靠性变得越来越重要。工艺的易变性和有限的缺陷容限导致器件在偏置和热应力下不稳定,同时扩大了关键参数的分布,例如介电击穿、漏电流和VT漂移。与传统的性能指标相比,二维晶体管的可靠性问题仍然相对缺乏研究。为了弥补这一差距,必须改进栅极堆叠技术,以同时提高器件性能和长期可靠性。此外,鉴于二维晶体管可靠性数据的匮乏,开发能够解释关键故障机制(尤其是介电击穿和偏置温度不稳定性)的预测性物理和统计模型至关重要,以指导工艺优化和系统级设计。

最先进的器件架构(例如 GAA-FET 和多桥沟道 FET)对栅极堆叠集成提出了更大的挑战和要求。多堆叠结构需要依次沉积二维沟道和牺牲层,并采用无损伤选择性蚀刻工艺。然而,尽管二维沟道具有很高的刚度,但机械应力和毛细力仍会导致沟道下垂。结构优化(包括源漏间距、内间隔、保护层和源漏夹紧)对于保持机械完整性至关重要。在垂直堆叠互补 FET (CFET) 或 3D 堆叠 FET 中,p-FET 集成在 n-FET 上,反之亦然,其挑战包括在极其狭窄的沟道间距内高度共形的 HKMG 沉积、使用中间介电层实现稳健的 n-FET 和 p-FET 隔离,以及通过替换金属栅极实现双功函数金属集成。

对于具有顶栅几何结构的场效应晶体管嵌入式栅极堆叠,高k界面层的引入和Dit的抑制对于增强场效应晶体管层上的电场以及确保可靠的极化切换以对抗陷阱介导的滞后效应至关重要。这些工艺,包括电介质沉积和场效应晶体管相稳定,必须与BEOL热预算兼容。因此,利用ISL进行界面应力工程,可以利用热膨胀失配和共结晶效应来降低场效应晶体管的结晶温度。

在栅极堆叠开发的同时,对二维薄膜生长的精确控制仍然是一项要求。关键参数,包括面积选择比、层数、载流子极性(n型和p型)和掺杂密度,必须仔细优化以满足集成需求,同时确保晶圆级(300毫米)的均匀性、高结晶度和低缺陷密度。对于垂直BEOL集成,二维生长和后处理必须在400°C以下进行,以防止互连扩散并保护底层。

从器件角度来看,接触工程是实现IRDS所定义性能目标的另一个重要领域。关键目标包括将接触电阻降低至量子极限,并实现n型和p型材料的纳米级接触转移长度,临界接触尺寸低于10纳米。除了最近开发的半金属接触之外,还需要具有更高热稳定性和化学稳定性的CMOS兼容接触技术。间隔掺杂和自对准方案进一步增强了可扩展性和器件性能。

最后,与超大规模高性能FEOL晶体管相结合,将二维晶体管集成到BEOL工艺中,为单片三维集成提供了一条充满希望的途径。这种逻辑、存储器和其他功能组件的垂直集成可以提高系统密度、带宽和能效。值得注意的是,采用低温可加工FE的FE-FET和FE-NAND为在BEOL层内实现“存内计算”功能提供了一种有前景的解决方案。垂直栅极堆栈集成的持续进步将在这一发展中发挥关键作用,为高度集成、节能和可扩展的 3D 电子系统铺平道路。

更新内容

一、修复bug,修改自动播放;优化产品用户体验。

二、 1.修复已知Bug。2.新服务。

三、修复已知bug;优化用户体验

四、1,交互全面优化,用户操作更加便捷高效;2,主题色更新,界面风格更加协调;3,增加卡片类个人数据

五、-千万商品随意挑选,大图展现商品细节-订单和物流查询实时同步-支持团购和名品特卖,更有手机专享等你抢-支付宝和银联多种支付方式,轻松下单,快捷支付-新浪微博,支付宝,QQ登录,不用注册也能购物-支持商品收藏,随时查询喜爱的商品和历史购物清单。

六、1.bug修复,提升用户体验;2.优化加载,体验更流程;3.提升安卓系统兼容性

七、1、修复部分机型bug;2、提高游戏流畅度;

相关版本

- 中文名:二维晶体管路线图

- 包名:com.ejiaqrp.dtgen

- MD5:P7ENQIWOC1RTO1T6EP

查看所有 0条评论>网友评论

- 更多>心动网络手游

-

- 更多>mod游戏

-

- 更多>像素rpg游戏

-

-

2025-10-23

1

-

2025-10-23

2

-

2025-10-23

3

-

2025-10-23

4

-

2025-10-23

5

-

2025-10-23

6

-

2025-10-23

7

-

2025-10-23

8

-

2025-10-23

9

-

2025-10-23

10

-

2025-10-23

11

-

2025-10-23

12

-

2025-10-23

13

-

2025-10-23

14

-

2025-10-23

15

-

2025-10-23

16

-

2025-10-23

17

-

2025-10-23

18

-

2025-10-23

19

-

2025-10-23

20

-

2025-10-23

21

-

2025-10-23

22

-

2025-10-23

23

-

2025-10-23

24

-

2025-10-23

25

-

2025-10-23

26

-

2025-10-23

27

-

2025-10-23

28

-

2025-10-23

29

-

2025-10-23

30

-

2025-10-23

31

-

2025-10-23

32

-

2025-10-23

33

-

2025-10-23

34

-

2025-10-23

35

-

2025-10-23

36

-

2025-10-23

37

-

2025-10-23

38

-

2025-10-23

39

-

2025-10-23

40

-

2025-10-23

41

-

2025-10-23

42

-

2025-10-23

43

-

2025-10-23

44

-

2025-10-23

45

-

2025-10-23

46

-

2025-10-23

47

-

2025-10-23

48

-

2025-10-23

49

-

2025-10-23

50

-

2025-10-23

51

-

2025-10-23

52

-

2025-10-23

53

-

2025-10-23

54

-

2025-10-23

55

-

2025-10-23

56

-

2025-10-23

57

-

2025-10-23

58

-

2025-10-23

59

-

2025-10-23

60

-

2025-10-23

61

-

2025-10-23

62

-

2025-10-23

63

-

2025-10-23

64

-

2025-10-23

65

-

2025-10-23

66

-

2025-10-23

67

-

2025-10-23

68

-

2025-10-23

69

-

2025-10-23

70

-

2025-10-23

71

-

2025-10-23

72

-

2025-10-23

73

-

2025-10-23

74

-

2025-10-23

75

-

2025-10-23

76

-

2025-10-23

77

-

2025-10-23

78

-

2025-10-23

79

-

2025-10-23

80

-

2025-10-23

81

-

2025-10-23

82

-

2025-10-23

83

-

2025-10-23

84

-

2025-10-23

85

-

2025-10-23

86

-

2025-10-23

87

-

2025-10-23

88

-

2025-10-23

89

-

2025-10-23

90

-

2025-10-23

91

-

2025-10-23

92

-

2025-10-23

93

-

2025-10-23

94

-

2025-10-23

95

-

2025-10-23

96

-

2025-10-23

97

-

2025-10-23

98

-

2025-10-23

99

-

2025-10-23

100

-

2025-10-23

101

-

2025-10-23

102

-

2025-10-23

103

-

2025-10-23

104

-

2025-10-23

105

-

2025-10-23

106

-

2025-10-23

107

-

2025-10-23

108

-

2025-10-23

109

-

2025-10-23

110

-

2025-10-23

111

-

2025-10-23

112

-

2025-10-23

113

-

2025-10-23

114

-

2025-10-23

115

-

2025-10-23

116

-

2025-10-23

117

-

2025-10-23

118

-

2025-10-23

119

-

2025-10-23

120

-

2025-10-23

121

-

2025-10-23

122

-

2025-10-23

123

-

2025-10-23

124

-

2025-10-23

125

-

2025-10-23

126

-

2025-10-23

127

-

2025-10-23

128

-

2025-10-23

129

-

2025-10-23

130

-

2025-10-23

131

-

2025-10-23

132

-

2025-10-23

133

-

2025-10-23

134

-

2025-10-23

135

-

2025-10-23

136

-

2025-10-23

137

-

2025-10-23

138

-

2025-10-23

139

-

2025-10-23

140

-

2025-10-23

141

-

2025-10-23

142

-

2025-10-23

143

-

2025-10-23

144

-

2025-10-23

145

-

2025-10-23

146

-

2025-10-23

147

-

2025-10-23

148

-

2025-10-23

149

-

2025-10-23

150

-

2025-10-23

151

-

2025-10-23

152

-

2025-10-23

153

-

2025-10-23

154

-

2025-10-23

155

-

2025-10-23

156

-

2025-10-23

157

-

2025-10-23

158

-

2025-10-23

159

-

2025-10-23

160

-

2025-10-23

161

-

2025-10-23

162

-

2025-10-23

163

-

2025-10-23

164

-

2025-10-23

165

-

2025-10-23

166

-

2025-10-23

167

-

2025-10-23

168

-

2025-10-23

169

-

2025-10-23

170

-

2025-10-23

171

-

2025-10-23

172

-

2025-10-23

173

-

2025-10-23

174

-

2025-10-23

175

-

2025-10-23

176

-

2025-10-23

177

-

2025-10-23

178

-

2025-10-23

179

-

2025-10-23

180

-

2025-10-23

181

-

2025-10-23

182

-

2025-10-23

183

-

2025-10-23

184

-

2025-10-23

185

-

2025-10-23

186

-

2025-10-23

187

-

2025-10-23

188

-

2025-10-23

189

-

2025-10-23

190

-

2025-10-23

191

-

2025-10-23

192

-

2025-10-23

193

-

2025-10-23

194

-

2025-10-23

195

-

2025-10-23

196

-

2025-10-23

197

-

2025-10-23

198

-

2025-10-23

199

-

2025-10-23

200

-

2025-10-23

201

-

2025-10-23

202

-

2025-10-23

203

-

2025-10-23

204

-

2025-10-23

205

-

2025-10-23

206

-

2025-10-23

207

-

2025-10-23

208

-

2025-10-23

209

-

2025-10-23

210

-

2025-10-23

211

-

2025-10-23

212

-

2025-10-23

213

-

2025-10-23

214

-

2025-10-23

215

-

2025-10-23

216

-

2025-10-23

217

-

2025-10-23

218

-

2025-10-23

219

-

2025-10-23

220

-

2025-10-23

221

-

2025-10-23

222

-

2025-10-23

223

-

2025-10-23

224

-

2025-10-23

225

-

2025-10-23

226

-

2025-10-23

227

-

2025-10-23

228

-

2025-10-23

229

-

2025-10-23

230

-

2025-10-23

231

-

2025-10-23

232

-

2025-10-23

233

-

2025-10-23

234

-

2025-10-23

235

-

2025-10-23

236

-

2025-10-23

237

-

2025-10-23

238

-

2025-10-23

239

-

2025-10-23

240

-

2025-10-23

241

-

2025-10-23

242

-

2025-10-23

243

-

2025-10-23

244

-

2025-10-23

245

-

2025-10-23

246

-

2025-10-23

247

-

2025-10-23

248

-

2025-10-23

249

-

2025-10-23

250

-

2025-10-23

251

-

2025-10-23

252

-

2025-10-23

253

-

2025-10-23

254

-

2025-10-23

255

-

2025-10-23

256

-

2025-10-23

257

-

2025-10-23

258

-

2025-10-23

259

-

2025-10-23

260

-

2025-10-23

261

-

2025-10-23

262

-

2025-10-23

263

-

2025-10-23

264

-

2025-10-23

265

-

2025-10-23

266

-

2025-10-23

267

-

2025-10-23

268

-

2025-10-23

269

-

2025-10-23

270

-

2025-10-23

271

-

2025-10-23

272

-

2025-10-23

273

-

2025-10-23

274

-

2025-10-23

275

-

2025-10-23

276

-

2025-10-23

277

-

2025-10-23

278

-

2025-10-23

279

-

2025-10-23

280

-

2025-10-23

281

-

2025-10-23

282

-

2025-10-23

283

-

2025-10-23

284

-

2025-10-23

285

-

2025-10-23

286

-

2025-10-23

287

-

2025-10-23

288

-

2025-10-23

289

-

2025-10-23

290

-

2025-10-23

291

-

2025-10-23

292

-

2025-10-23

293

-

2025-10-23

294

-

2025-10-23

295

-

2025-10-23

296

-

2025-10-23

297

-

2025-10-23

298

-

2025-10-23

299

-

2025-10-23

300

-

2025-10-23

301

-

2025-10-23

302

-

2025-10-23

303

-

2025-10-23

304

-

2025-10-23

305

-

2025-10-23

306

-

2025-10-23

307

-

2025-10-23

308

-

2025-10-23

309

-

2025-10-23

310

-

2025-10-23

311

-

2025-10-23

312

-

2025-10-23

313

-

2025-10-23

314

-

2025-10-23

315

-

2025-10-23

316

-

2025-10-23

317

-

2025-10-23

318

-

2025-10-23

319

-

2025-10-23

320

-

2025-10-23

321

-

2025-10-23

322

-

2025-10-23

323

-

2025-10-23

324

-

2025-10-23

325

-

2025-10-23

326

-

2025-10-23

327

-

2025-10-23

328

-

2025-10-23

329

-

2025-10-23

330

-

2025-10-23

331

-

2025-10-23

332

-

2025-10-23

333

-

2025-10-23

334

-

2025-10-23

335

-

2025-10-23

336

-

2025-10-23

337

-

2025-10-23

338

-

2025-10-23

339

-

2025-10-23

340

-

2025-10-23

341

-

2025-10-23

342

-

2025-10-23

343

-

2025-10-23

344

-

2025-10-23

345

-

2025-10-23

346

-

2025-10-23

347

-

2025-10-23

348

-

2025-10-23

349

-

2025-10-23

350

-

2025-10-23

351

-

2025-10-23

352

-

2025-10-23

353

-

2025-10-23

354

-

2025-10-23

355

-

2025-10-23

356

-

2025-10-23

357

-

2025-10-23

358

-

2025-10-23

359

-

2025-10-23

360

-

2025-10-23

361

-

2025-10-23

362

-

2025-10-23

363

-

2025-10-23

364

-

2025-10-23

365

-

2025-10-23

366

-

2025-10-23

367

-

2025-10-23

368

-

2025-10-23

369

-

2025-10-23

370

-

2025-10-23

371

-

2025-10-23

372

-

2025-10-23

373

-

2025-10-23

374

-

2025-10-23

375

-

2025-10-23

376

-

2025-10-23

377

-

2025-10-23

378

-

2025-10-23

379

-

2025-10-23

380

-

2025-10-23

381

-

2025-10-23

382

-

2025-10-23

383

-

2025-10-23

384

-

2025-10-23

385

-

2025-10-23

386

-

2025-10-23

387

-

2025-10-23

388

-

2025-10-23

389

-

2025-10-23

390

-

2025-10-23

391

-

2025-10-23

392

-

2025-10-23

393

-

2025-10-23

394

-

2025-10-23

395

-

2025-10-23

396

-

2025-10-23

397

-

2025-10-23

398

-

2025-10-23

399

-

2025-10-23

400

-

2025-10-23

1

-

2025-10-23

2

-

2025-10-23

3

-

2025-10-23

4

-

2025-10-23

5

-

2025-10-23

6

-

2025-10-23

7

-

2025-10-23

8

-

2025-10-23

9

-

2025-10-23

10

-

2025-10-23

11

-

2025-10-23

12

-

2025-10-23

13

-

2025-10-23

14

-

2025-10-23

15

-

2025-10-23

16

-

2025-10-23

17

-

2025-10-23

18

-

2025-10-23

19

-

2025-10-23

20

-

2025-10-23

21

-

2025-10-23

22

-

2025-10-23

23

-

2025-10-23

24

-

2025-10-23

25

-

2025-10-23

26

-

2025-10-23

27

-

2025-10-23

28

-

2025-10-23

29

-

2025-10-23

30

-

2025-10-23

31

-

2025-10-23

32

-

2025-10-23

33

-

2025-10-23

34

-

2025-10-23

35

-

2025-10-23

36

-

2025-10-23

37

-

2025-10-23

38

-

2025-10-23

39

-

2025-10-23

40

-

2025-10-23

41

-

2025-10-23

42

-

2025-10-23

43

-

2025-10-23

44

-

2025-10-23

45

-

2025-10-23

46

-

2025-10-23

47

-

2025-10-23

48

-

2025-10-23

49

-

2025-10-23

50

-

2025-10-23

51

-

2025-10-23

52

-

2025-10-23

53

-

2025-10-23

54

-

2025-10-23

55

-

2025-10-23

56

-

2025-10-23

57

-

2025-10-23

58

-

2025-10-23

59

-

2025-10-23

60

-

2025-10-23

61

-

2025-10-23

62

-

2025-10-23

63

-

2025-10-23

64

-

2025-10-23

65

-

2025-10-23

66

-

2025-10-23

67

-

2025-10-23

68

-

2025-10-23

69

-

2025-10-23

70

-

2025-10-23

71

-

2025-10-23

72

-

2025-10-23

73

-

2025-10-23

74

-

2025-10-23

75

-

2025-10-23

76

-

2025-10-23

77

-

2025-10-23

78

-

2025-10-23

79

-

2025-10-23

80

-

2025-10-23

81

-

2025-10-23

82

-

2025-10-23

83

-

2025-10-23

84

-

2025-10-23

85

-

2025-10-23

86

-

2025-10-23

87

-

2025-10-23

88

-

2025-10-23

89

-

2025-10-23

90

-

2025-10-23

91

-

2025-10-23

92

-

2025-10-23

93

-

2025-10-23

94

-

2025-10-23

95

-

2025-10-23

96

-

2025-10-23

97

-

2025-10-23

98

-

2025-10-23

99

-

2025-10-23

100